www.ti.com

# DS50PCI402 2.5 Gbps / 5.0 Gbps 4 Lane PCI Express Repeater with Equalization and De-Emphasis

Check for Samples: DS50PCI402

#### **FEATURES**

- Input and Output signal conditioning increases PCle reach in backplanes and cables

- 0.09 UI of residual deterministic jitter at 5Gbps after 42" of FR4 (with Input EQ)

- 0.11 UI of residual deterministic jitter at 5Gbps after 7m of PCle Cable (with Input EQ)

- 0.09 UI of residual deterministic jitter at 5Gbps with 28" of FR4 (with Output DE)

- 0.13 UI of residual deterministic jitter at 5Gbps with 7m of PCIe Cable (with Output DE)

- Adjustable Transmit VOD 800 to 1200mVp-p

- Automatic and manual Receiver Detection and input termination control circuitry

- Automatic power management on an individual lane basis via SMBus

- Adjustable electrical idle detect threshold.

- Data rate optimized 3-stage equalization to 27 dB gain

- Data rate optimized 6-level 0 to 12 dB transmit de-emphasis

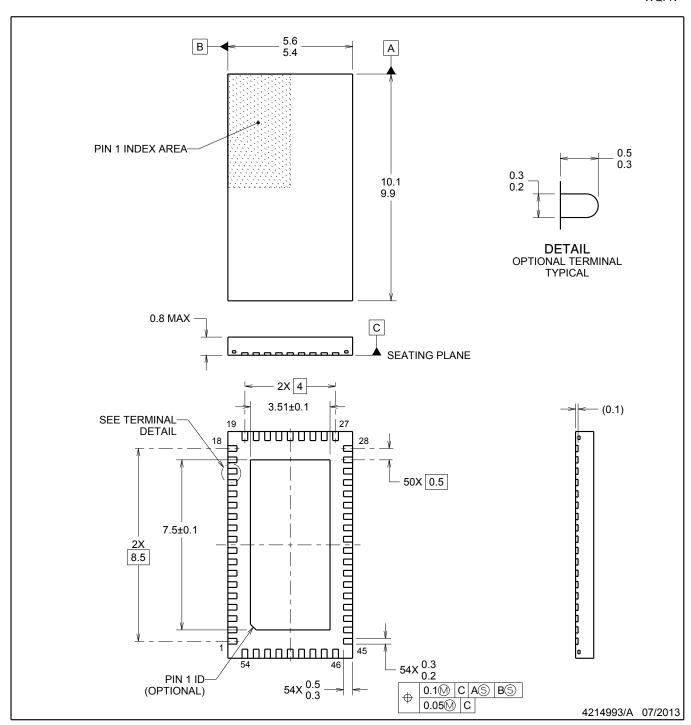

- Flow-thru pinout in 10mmx5.5mm 54-pin leadless WQFN package

- Single supply operation at 2.5V

- >6kV HBM ESD rating

- -10 to 85°C operating temperature range

#### DESCRIPTION

The DS50PCI402 is a low power, 4 lane bidirectional buffer/equalizer designed specifically for PCI Express Gen1 and Gen2 applications. The device performs both receive equalization and transmit de-emphasis, allowing maximum flexibility of physical placement within a system. The receiver is capable of opening an input eye that is completely closed due to intersymbol interference (ISI) induced by the interconnect medium.

The transmitter de-emphasis level can be set by the user depending on the distance from the DS50PCI402 to the PCI Express endpoint. The DS50PCI402 contains PCI Express specific functions such as Transmit Idle, RX Detection, and Beacon signal pass through.

The device provides automatic receive detection circuitry which controls the input termination impedance. By automatically reflecting the current load impedance seen on the outputs back to the corresponding inputs the DS50PCI402 becomes completely transparent to both the PCIe root complex and endpoint. An internal rate detection circuit is included to detect if an incoming data stream is at Gen2 data rates, and adjusts the de-emphasis on it's output accordingly. The signal conditioning provided by the device allows systems to upgrade from Gen1 data rates to Gen2 without reducing their physical reach. This is true for FR4 applications such as backplanes, as well as cable interconnect.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

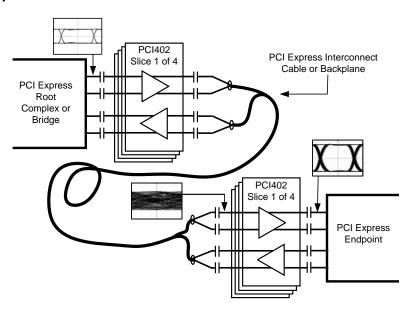

## **Typical Application**

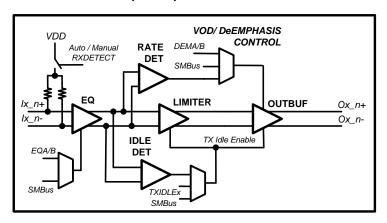

## **Block Diagram - Detail View Of Channel (1 of 8)**

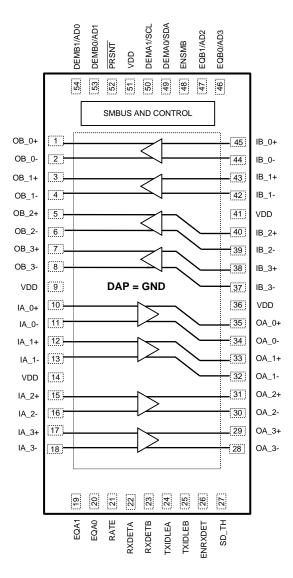

#### Pin Diagram

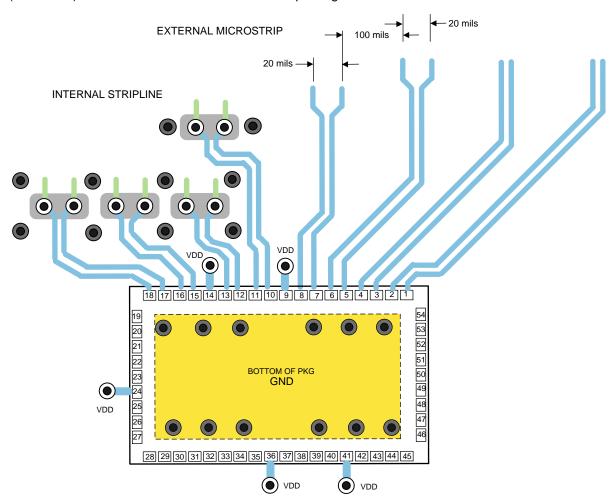

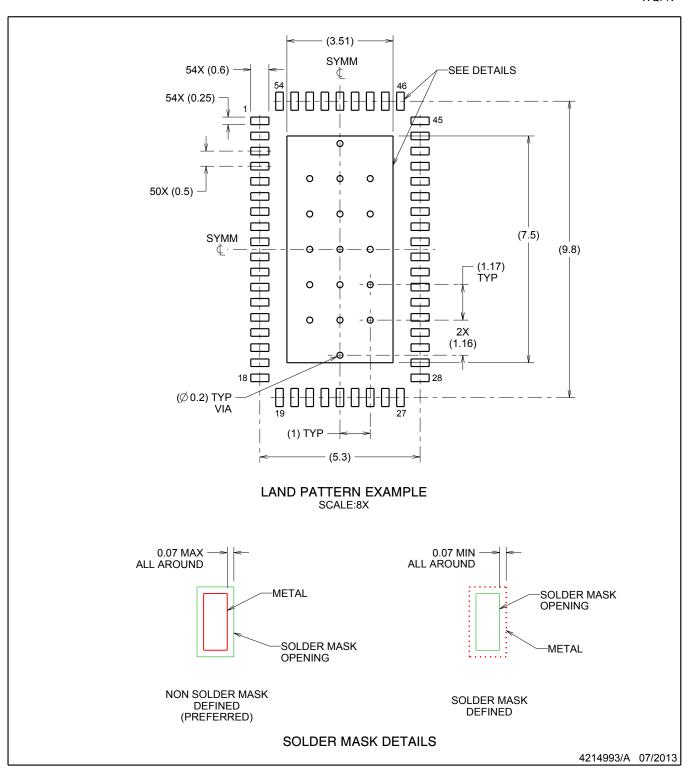

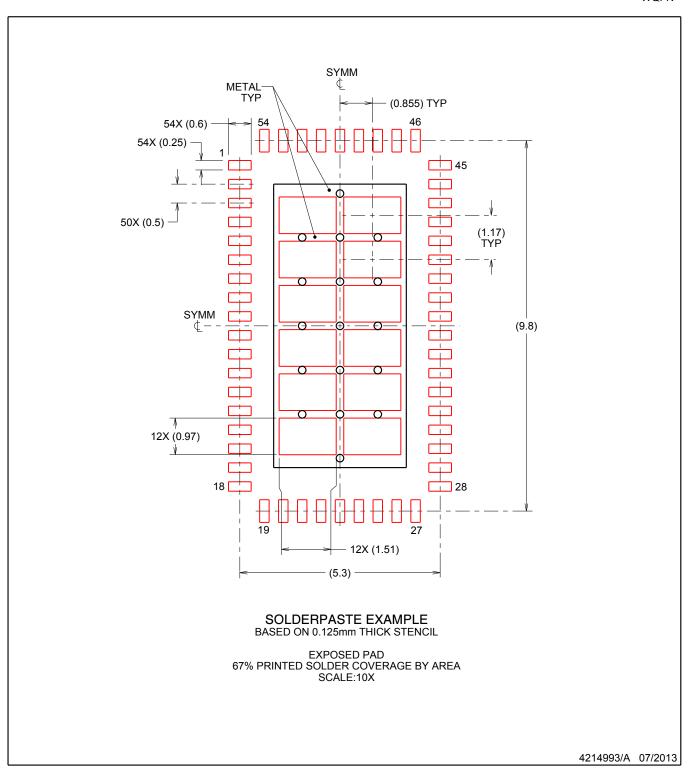

The center DAP on the package bottom is the device GND connection. This pad must be connected to GND through multiple (minimum of 8) vias to ensure optimal electrical and thermal performance.

#### DS50PCI402 Pin Diagram 54 lead

#### **Table 1. Pin Descriptions**

|                                                                 |                                      | Table 1.                             | Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------|--------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                        | Pin Number                           | I/O,<br>Type <sup>(1)(2)(3)(4)</sup> | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Differential High Speed I/                                      | 'O's                                 |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| IA_0+, IA_0-,<br>IA_1+, IA_1-,<br>IA_2+, IA_2-,<br>IA_3+, IA_3- | 10, 11<br>12, 13<br>15, 16<br>17, 18 | I, CML                               | Inverting and non-inverting CML differential inputs to the equalizer. A gated on-chip $50\Omega$ termination resistor connects INA_0+ to VDD and INA_0- to VDD when enabled.                                                                                                                                                                                                                                                                                                                                                                  |

| OA_0+, OA_0-,<br>OA_1+, OA_1-,<br>OA_2+, OA_2-,<br>OA_3+, OA_3- | 35, 34<br>33, 32<br>31, 30<br>29, 28 | O,LPDS                               | Inverting and non-inverting low power differential signal (LPDS) $50\Omega$ driver outputs with de-emphasis. Compatible with AC coupled CML inputs.                                                                                                                                                                                                                                                                                                                                                                                           |

| IB_0+, IB_0-,<br>IB_1+, IB_1-,<br>IB_2+, IB_2-,<br>IB_3+, IB_3- | 45, 44<br>43, 42<br>40, 39<br>38, 37 | I, CML                               | Inverting and non-inverting CML differential inputs to the equalizer. A gated on-chip $50\Omega$ termination resistor connects INB_0+ to VDD and INB_0- to VDD when enabled.                                                                                                                                                                                                                                                                                                                                                                  |

| OB_0+, OB_0-,<br>OB_1+, OB_1-,<br>OB_2+, OB_2-,<br>OB_3+, OB_3- | 1, 2<br>3, 4<br>5, 6<br>7, 8         | O,LPDS                               | Inverting and non-inverting low power differential signal (LPDS) $50\Omega$ driver outputs with de-emphasis. Compatible with AC coupled CML inputs.                                                                                                                                                                                                                                                                                                                                                                                           |

| Control Pins — Shared (I                                        | VCMOS)                               |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ENSMB                                                           | 48                                   | I, LVCMOS<br>w/internal<br>pulldown  | System Management Bus (SMBus) enable pin. When pulled high provide access internal digital registers that are a means of auxiliary control for such functions as equalization, deemphasis, VOD, rate, and idle detection threshold. When pulled low, access to the SMBus registers are disabled and SMBus function pins are used to control the Equalizer and De-Emphasis. Please refer to SYSTEM MANAGEMENT BUS (SMBUS) AND CONFIGURATION REGISTERS and Electrical Characteristics — Serial Management Bus Interface for detail information. |

| ENSMB = 1 (SMBUS MOD                                            | DE)                                  |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SCL                                                             | 50                                   | I, LVCMOS                            | ENSMB = 1 SMBUS clock input pin is enabled. External pull-up resistor maybe needed. Refer to R <sub>TERM</sub> in the SMBus specification.                                                                                                                                                                                                                                                                                                                                                                                                    |

| SDA                                                             | 49                                   | I, LVCMOS,<br>O, Open Drain          | ENSMB = 1 The SMBus bi-directional SDA pin is enabled. Data input or open drain output. External pull-up resistor is required. Refer to R <sub>TERM</sub> in the SMBus specification.                                                                                                                                                                                                                                                                                                                                                         |

| AD0-AD3                                                         | 54, 53, 47, 46                       | I, LVCMOS<br>w/internal<br>pulldown  | ENSMB = 1 SMBus Slave Address Inputs. In SMBus mode, these pins are the user set SMBus slave address inputs. See section — SYSTEM MANAGEMENT BUS (SMBUS) AND CONFIGURATION REGISTERS for additional information.                                                                                                                                                                                                                                                                                                                              |

| ENSMB = 0 (NORMAL PIN                                           | N MODE)                              |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| EQA0, EQA1<br>EQB0, EQB1                                        | 20, 19<br>46, 47                     | I,FLOAT,<br>LVCMOS                   | EQA/B ,0/1 controls the level of equalization of the A/B sides as shown in Table 2. The EQA/B pins are active only when ENSMB is de-asserted (Low). Each of the 4 A/B channels have the same level unless controlled by the SMBus control registers. When ENSMB goes high the SMBus registers provide independent control of each lane, and the EQB0/B1 pins are converted to SMBUS AD2/AD3 inputs.                                                                                                                                           |

| DEMA0, DEMA1<br>DEMB0, DEMB1                                    | 49, 50<br>53, 54                     | I,FLOAT,<br>LVCMOS                   | DEMA/B ,0/1 controls the level of de-emphasis of the A/B sides as shown in Table 5. The DEMA/B pins are only active when ENSMB is deasserted (Low). Each of the 4 A/B channels have the same level unless controlled by the SMBus control registers. When ENSMB goes High the SMBus registers provide independent control of each lane and the DEM pins are converted to SMBUS AD0/AD1 and SCL/SDA inputs.                                                                                                                                    |

Submit Documentation Feedback

Copyright © 2010–2013, Texas Instruments Incorporated

<sup>(1)</sup> FLOAT = 3rd input state, don't drive pin. Pin is internally biased to mid level with 50 kΩ pull-up/pull-down. If high Z output not available, drive input to VDD/2 to assert mid level state.

<sup>(2)</sup> Internal pulldown = Internal 30 k $\Omega$  pull-down resistor to GND is present on the input.

<sup>(3)</sup> LVCMOS inputs without the "Float" conditions must be driven to a logic Low or High at all times or operation is not ensured.

<sup>(4)</sup> Input edge rate for LVCMOS/FLOAT inputs must be faster than 50 ns from 10–90%.

## **Table 1. Pin Descriptions (continued)**

| Pin Name              | Pin Number       | I/O,<br>Type <sup>(1)(2)(3)(4)</sup> | Pin Description                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------|------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RATE                  | 21               | I,FLOAT,<br>LVCMOS                   | RATE control pin controls the pulse width of de-emphasis of the output. A Low forces Gen1 (2.5Gbps), High forces Gen 2 (5Gbps), Open/Floating the rate is internally detected after each exit from idle and the pulse width is set appropriately. When ENSMBUS= 1 this pin is disabled and the RATE function is controlled internally by the SMBUS registers. Refer to Table 5. |

| Control Pins — Both N | lodes (LVCMOS)   |                                      |                                                                                                                                                                                                                                                                                                                                                                                 |

| RXDETA,RXDETB         | 22,23            | I, LVCMOS<br>w/internal<br>pulldown  | The RXDET pins in combination with the ENRXDET pin controls the receiver detect function. Depending on the input level, a $50\Omega$ or $>50K\Omega$ termination to the power rail is enabled. Refer to Table 7.                                                                                                                                                                |

| PRSNT                 | 52               | I, LVCMOS                            | Cable Present Detect input. High when a cable is not present per PCle Cabling Spec. 1.0. Puts part into low power mode. When low (normal operation) part is enabled.                                                                                                                                                                                                            |

| ENRXDET               | 26               | I, LVCMOS<br>w/internal<br>pulldown  | Enables pin control of receiver detect function. The default is automatic RXDET using the internal pulldown. Pin must be pulled high for manual RXDETA/B operation. Controls individual A and B sides. Refer to Table 7.                                                                                                                                                        |

| TXIDLEA,TXIDLEB       | 24,25            | I, FLOAT,<br>LVCMOS                  | Controls the electrical idle function on corresponding outputs when enabled. H= electrical Idle, Float=autodetect (Idle on input passed to output), L=Idle squelch disabled as shown in Table 6.                                                                                                                                                                                |

| Analog                |                  |                                      |                                                                                                                                                                                                                                                                                                                                                                                 |

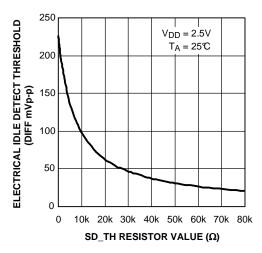

| SD_TH                 | 27               | I, ANALOG                            | Threshold select pin for electrical idle detect threshold. Float pin for default 130mV DIFF p-p, otherwise connect resistor from SD_TH to GND to set threshold voltage as shown in Table 7.                                                                                                                                                                                     |

| Power                 |                  |                                      |                                                                                                                                                                                                                                                                                                                                                                                 |

| VDD                   | 9, 14,36, 41, 51 | Power                                | Power supply pins CML/analog.                                                                                                                                                                                                                                                                                                                                                   |

| GND                   | DAP              | Power                                | Ground pad (DAP - die attach pad).                                                                                                                                                                                                                                                                                                                                              |

#### FUNCTIONAL DESCRIPTION

The DS50PCI402 is a low power media compensation 4 lane repeater optimized for PCI Express Gen 1 and Gen 2 media including lossy FR-4 printed circuit board backplanes and balanced cables. The DS50PCI402 operates in two modes: Pin Control Mode (ENSMB = 0) and SMBus Mode (ENSMB = 1).

#### Pin Control Mode:

When in pin mode (ENSMB = 0) , the repeater is configurable with external pins. Equalization and de-emphasis can be selected via pin for each side independently. When de-emphasis is asserted VOD is automatically increased per the De-Emphasis table below for improved performance over lossy media. The receiver detect pins RXDETA/B provide manual control for input termination ( $50\Omega$  or  $>50K\Omega$ ). Rate optimization is also pin controllable, with pin selections for 2.5Gbps, 5Gbps, and auto detect. The receiver electrical idle detect threshold is also programmable via an optional external resistor on the SD\_TH pin.

#### SMBUS Mode:

When in SMBus mode the equalization, de-emphasis, and termination disable features are all programmable on a individual lane basis, instead of grouped by sides as in the pin mode case. Upon assertion of ENSMB the RATE, EQx and DEMx functions revert to register control immediately. The EQx and DEMx pins are converted to AD0-AD3 SMBus address inputs. The other external control pins remain active unless their respective registers are written to and the appropriate override bit is set, in which case they are ignored until ENSMB is driven low. On powerup and when ENSMB is driven low all registers are reset to their default state. If PRSNT is asserted while ENSMB is high, the registers retain their current state.

Equalization settings accessible via the pin controls were chosen to meet the needs of most PCIe applications. If additional fine tuning or adjustment is needed, additional equalization settings can be accessed via the SMBus registers. Each input has a total of 24 possible equalization settings. The tables show a typical gain for each gain stage (GST[1:0]) and boost level (BST[2:0]) combination. When using SMBus mode, the Equalization and De-Emphasis levels are set using registers.

Table 2. Equalization Settings with GST=1 for Pins or SMBus Registers

| E04(             | <b>500</b> (     | EQ Setting   |              | EQ Gain (dB) |         |                                                  |

|------------------|------------------|--------------|--------------|--------------|---------|--------------------------------------------------|

| EQ1 <sup>(</sup> | EQ0 <sup>(</sup> | GST[1<br>:0] | BST[2:<br>0] | 1.25 GHz     | 2.5 GHz | Suggested Use                                    |

| F                | F                | 00           | 000          | 0            | 0       | Bypass - Default Setting                         |

|                  |                  | 01           | 000          | 1.6          | 3.2     |                                                  |

|                  |                  | 01           | 001          | 2.1          | 4.2     |                                                  |

| 1                | 1                | 01           | 010          | 2.6          | 5.0     | 8" FR4 (6-mil trace) or < 1m (28 AWG) PCIe cable |

|                  |                  | 01           | 011          | 3.2          | 5.9     |                                                  |

|                  |                  | 01           | 100          | 4.0          | 7.3     |                                                  |

|                  |                  | 01           | 101          | 4.9          | 7.9     |                                                  |

|                  |                  | 01           | 110          | 5.4          | 8.5     |                                                  |

|                  |                  | 01           | 111          | 5.6          | 9.0     |                                                  |

<sup>(1)</sup> F=Float (don't drive pin, each float pin has an internal 50K Ohm resistor to VDD and GND), 1=High, 0=Low

Table 3. Equalization Settings with GST=2 for Pins or SMBus Registers

| EQ1 <sup>(</sup> | EOO( | EQ0 <sup>(</sup> EQ Setting EQ Gain (dB) |              |          |         |                                                 |

|------------------|------|------------------------------------------|--------------|----------|---------|-------------------------------------------------|

| 1)               | 1)   | GST[1<br>:0]                             | BST[2:<br>0] | 1.25 GHz | 2.5 GHz | Suggested Use                                   |

| 0                | 0    | 10                                       | 000          | 3.8      | 7.6     | 14" FR4 (6-mil trace) or 1m (28 AWG) PCIe cable |

|                  |      | 10                                       | 001          | 5.1      | 9.9     |                                                 |

| F                | 0    | 10                                       | 010          | 6.4      | 11.6    | 20" FR4 (6-mil trace) or 5m (26 AWG) PCIe cable |

|                  |      | 10                                       | 011          | 7.6      | 13.5    |                                                 |

|                  |      | 10                                       | 100          | 9.5      | 16.1    |                                                 |

| F                | 1    | 10                                       | 101          | 11.3     | 17.5    | 40" FR4 (6-mil trace) or 9m (24 AWG) PCIe cable |

(1) F=Float (don't drive pin, each float pin has an internal 50K Ohm resistor to VDD and GND), 1=High, 0=Low

#### Table 3. Equalization Settings with GST=2 for Pins or SMBus Registers (continued)

| E04(             | EQ0 <sup>(</sup> | EQ Setting   |              | EQ Ga    | in (dB) |                                                  |

|------------------|------------------|--------------|--------------|----------|---------|--------------------------------------------------|

| EQ1 <sup>(</sup> | 1)               | GST[1<br>:0] | BST[2:<br>0] | 1.25 GHz | 2.5 GHz | Suggested Use                                    |

|                  |                  | 10           | 110          | 12.3     | 18.6    |                                                  |

| 0                | 1                | 10           | 111          | 12.8     | 19.8    | 50" FR4 (6-mil trace) or 10m (24 AWG) PCIe cable |

Table 4. Equalization Settings with GST=3 for Pins or SMBus Registers

| E04(             | EQ0 <sup>(</sup> | EQ S         | Setting      | EQ Gain (dB) |         |                                                 |

|------------------|------------------|--------------|--------------|--------------|---------|-------------------------------------------------|

| EQ1 <sup>(</sup> | 1)               | GST[1<br>:0] | BST[2:<br>0] | 1.25 GHz     | 2.5 GHz | Suggested Use                                   |

|                  |                  | 11           | 000          | 6.4          | 12.2    |                                                 |

| 1                | 0                | 11           | 001          | 8.5          | 15.6    | 30" FR4 (6-mil trace) or 7m (24 AWG) PCIe cable |

|                  |                  | 11           | 010          | 10.4         | 18.3    |                                                 |

| 0                | F                | 11           | 011          | 12.4         | 21.3    | 15m (24 AWG) PCIe cable                         |

|                  |                  | 11           | 100          | 15.2         | 25.0    |                                                 |

| 1                | F                | 11           | 101          | 18.1         | 27.2    | > 15m (24 AWG) PCIe cable                       |

|                  |                  | 11           | 110          | 19.6         | 28.8    |                                                 |

|                  |                  | 11           | 111          | 20.2         | 30.7    |                                                 |

<sup>(1)</sup> F=Float (don't drive pin, each float pin has an internal 50K Ohm resistor to VDD and GND), 1=High, 0=Low

The De-Emphasis level must be set when in SMBus mode. See SMBus TRANSACTIONS section and Table 10 for specific De-Emphasis values.

Table 5. De-Emphasis Input Select Pins for A and B ports (3-Level Input)

| RATE | DEM1<br>(1) | DEM0 <sup>(1</sup> | Typical De-<br>Emphasis Level | Typical DE Pulse<br>Width | Typical VOD | Suggested Use                                                          |

|------|-------------|--------------------|-------------------------------|---------------------------|-------------|------------------------------------------------------------------------|

| 0/F  | 0           | 0                  | 0dB                           | 0ps                       | 1000mV      |                                                                        |

| 0/F  | 0           | 1                  | -3.5dB                        | 400ps                     | 1000mV      | 8 inches FR4 (6-mil trace) or less than 1<br>meter (28 AWG) PCIe cable |

| 0/F  | 1           | 0                  | -6dB                          | 400ps                     | 1000mV      |                                                                        |

| 0/F  | 1           | 1                  | -6dB                          | 400ps enhanced            | 1000mV      | 15 inches FR4 (6-mil trace)                                            |

| 0/F  | 0           | F                  | -9dB                          | 400ps enhanced            | 1000mV      |                                                                        |

| 0/F  | 1           | F                  | -12dB                         | 400ps enhanced            | 1000mV      |                                                                        |

| 0/F  | F           | 0                  | -9dB                          | 400ps enhanced            | 1200mV      | 30 inches FR4 (6-mil trace)                                            |

| 0/F  | F           | 1                  | -12dB                         | 400ps enhanced            | 1400mV      | 40 inches FR4 (6-mil trace)                                            |

| 0/F  | F           | F                  | Reserved, don't use           |                           |             |                                                                        |

| 1/F  | 0           | 0                  | 0dB                           | 0ps                       | 1000mV      |                                                                        |

| 1/F  | 0           | 1                  | -3.5dB                        | 200ps                     | 1000mV      |                                                                        |

| 1/F  | 1           | 0                  | -6dB                          | 200ps                     | 1000mV      |                                                                        |

| 1/F  | 1           | 1                  | -6dB                          | 200ps enhanced            | 1000mV      | 10 inches FR4 (6-mil trace)                                            |

| 1/F  | 0           | F                  | -9dB                          | 200ps enhanced            | 1000mV      |                                                                        |

| 1/F  | 1           | F                  | -12dB                         | 200ps enhanced            | 1000mV      |                                                                        |

| 1/F  | F           | 0                  | -9dB                          | 200ps enhanced            | 1200mV      | 20 inches FR4 (6-mil trace)                                            |

| 1/F  | F           | 1                  | -12dB                         | 200ps enhanced            | 1400mV      | 30 inches FR4 (6-mil trace)                                            |

| 1/F  | F           | F                  | Reserved, don't use           |                           |             |                                                                        |

<sup>(1)</sup> F=Float (don't drive pin - (each float pin has an internal 50K Ohm resistor to VDD and GND). Enhanced DE Pulse width provides additional de-emphasis on second bit. VOD = Voltage Output Differential amplitude. When RATE is floated (F=Auto Rate Detection Active) DE Level and Pulse Width settings follow detected RATE. RATE=0 is 2.5GBps, RATE=1 is 5 GBps

#### Table 6. Idle Control (3-Level Input)

| TXIDLEA/B | Function                                                                                                                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0         | This state is for lossy media, dedicated Idle threshold detect circuit disabled, output follows input based on EQ settings. Idle state not ensured.                                                    |

| Float     | Float enables automatic idle detection. Idle on the input is passed to the output. This is the recommended default state. Output driven to Idle if diff input signal less than value set by SD_TH pin. |

| 1         | Manual override, output forced to Idle. Diff inputs are ignored.                                                                                                                                       |

Table 7. Receiver Electrical Idle Detect Threshold Adjust (Analog input - Connect Resistor to GND or Float)

| SD_TH resistor value (Ω) (connect from pin to GND) <sup>(1)</sup> | Typical Receiver Electrical Idle Detect Threshold (DIFF p-p) |  |  |

|-------------------------------------------------------------------|--------------------------------------------------------------|--|--|

| Float (no resistor required)                                      | 130mV (default condition)                                    |  |  |

| 0                                                                 | 225mV                                                        |  |  |

| 80K                                                               | 20mV                                                         |  |  |

(1) SD\_TH resistor value can be set from 0 through 80K Ohms to achieve desired idle detect threshold, see Figure 1. 8K Ohm is approx 130mV.

Figure 1. Typical Idle threshold vs SD TH resistor value

#### **Receiver Detection**

The Rx detection process is a feature that can set the number of active channels on the DS50PCI402. By sensing the presence of a valid PCIe load on the output, the channel can be automatically enabled for operation. This allows the DS50PCI402 to configure inself to the proper lane width, whether it is a 4-lane, 2-lane, or 1-lane PCIe link.

Automatic Rx Detection is enabled by a combination of PRSNT# and ENRXDET inputs. When these inputs are set low, Automatic Rx Detection is enabled, cycling of the PRSNT# pin will reset the Rx detection circuitry, initiating a new receiver detection sequence. Pulling the ENRXDET input to logic 1, allows for manual control of the input termination.

The table below summarizes control pin and receiver detect operation for the DS50PCI402.

#### Table 8. Receiver Detect Pins for A and B ports (LVCMOS inputs)

| PRSNT# | ENRXDET | RXDETA/B | Input<br>Termination    | Termination sensed on<br>Output | Function                                                                                                                                                                                                                                                                                                 |

|--------|---------|----------|-------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0       | 0        | $>$ 50K $\Omega$ to VDD | Hi - Z                          | Automatic RXDET: Rx detection state machine                                                                                                                                                                                                                                                              |

|        |         |          | 50Ω                     | PCle Input                      | enabled. Outputs will test for the presence of a receiver input every 12 msec until detection occurs. Input termination remains >50K $\Omega$ to VDD until receiver is detected. Once receiver is detected, input impedance to VDD is 50 $\Omega$ .                                                      |

| 0      | 0       | 1        | $>$ 50K $\Omega$ to VDD | Hi - Z                          | Automatic RXDET: Rx detection state machine                                                                                                                                                                                                                                                              |

|        |         |          | 50Ω                     | PCIe Input                      | enabled. Outputs will test for the presence of a receiver input every 12 msec for 600 msec and then stop. Input termination remains >50K $\Omega$ to VDD until receiver is detected. Once receiver is detected, input impedance to VDD is 50 $\Omega$ . Restart detection if RXDETA/B is pulsed lowhigh. |

| 0      | 1       | 0        | >50KΩ to VDD            | X                               | Manual RXDET: Rx detection state machine disabled. Input termination >50KΩ. Associated output channels in low power idle mode.                                                                                                                                                                           |

| 0      | 1       | 1        | 50Ω                     | X                               | Manual RXDET: Rx detection state machine disabled. Input termination $50\Omega$ . Associated output channels set to active.                                                                                                                                                                              |

| 1      | X       | X        | >50KΩ to VDD            | Х                               | Power down mode: Input termination >50KΩ. Associated output channels off. Part in power saving mode. PRSNT# should be held high for a minimum of 5 us to ensure complete analog power down. The Automatic RXDET functionality will be re-initialized on the falling edge of PRSNT#.                      |

#### **RX Detect: Range of Operation**

The Rx detection process used in the DS50PCI402 is designed to be fully compliant with the PCIe 2.0 base specification. The receiver detection circuitry will accurately detect a receiver when both conditions listed below are true:

- DS50PCI402 within Recommended Operating Range for Temperature and Supply Voltage

- For receiver Z<sub>RX-DC</sub> = 40 (min) to 60 (max) Ohms

Note: To ensure robust system operation, the DS50PCI402 will only signal a valid receiver detection if both halves of the differential output pair detect a proper 40 - 60 Ohm receiver impedance. If the receiver detection circuitry senses a load impedance greater than Z<sub>RX-DC</sub> on either trace of a differential pair, it will be interpreted as no termination load present (i.e. the corresponding DS50PCI402 input termination will remain High-Z).

#### Manual Control Of RXDETA/B In A PCIe Environment

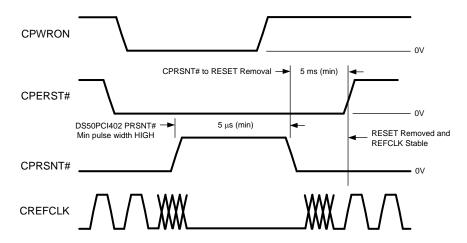

In some cases manual control of RXDETA/B may be desirable. In order for upstream and downstream PCIe subsystems to communicate in a cabling environment, the PCIe specification includes several auxiliary or sideband signals to manage system-level functionality or implementation. Similar methods are used in backplane applications, but the exact implementation falls outside the PCIe standard. Initial communication from the downstream subsystem to the upstream subsystem is done with the CPRSNT# auxiliary signal. The CPRSNT# signal is asserted Low by the downstream componentry after the "Power Good" condition has been established. This mechanism allows for the upstream subsystem to determine whether the power is good within the downstream subsystem, enable the reference clock, and initiate the Link Training Sequence.

Figure 2. Typical PCIe System Timing

The signals shown in the graphic could be easily replicated within the downstream subsystem and used to externally control the common mode input termination impedance on the DS50PCI402. Often an onboard microcontroller will be used to handle events like power-up, power-down, power saving modes, and hot insertion. The microcontroller would use the same information to determine when to enable and disable the DS50PCI402 input termination. In applications that require SMBus control, the microcontroller could also delay any response to the upstream subsystem to allow sufficient time to correctly program the DS50PCI402 and other devices on the board.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## Absolute Maximum Ratings (1)(2)

| Absolute Maximum Natings                            |                       |

|-----------------------------------------------------|-----------------------|

| Supply Voltage (VDD)                                | -0.5V to +3.0V        |

| LVCMOS Input/Output Voltage                         | -0.5V to +4.0V        |

| CML Input Voltage                                   | -0.5V to (VDD+0.5V)   |

| CML Input Current                                   | -30 to +30 mA         |

| LPDS Output Voltage                                 | -0.5V to (VDD+0.5V)   |

| Analog (SD_TH) <sup>(3)</sup>                       | -0.5V to (VDD+0.5V)   |

| Junction Temperature                                | +125°C                |

| Storage Temperature                                 | -40°C to +125°C       |

| Lead Temperature Range                              |                       |

| Maximum Package Power Dissipation at 25°C           |                       |

| NJY Package                                         | 4.21 W                |

| Derate NJY Package                                  | 52.6mW/°C above +25°C |

| ESD Rating                                          |                       |

| HBM, STD - JESD22-A114C                             | ≥6 kV                 |

| MM, STD - JESD22-A115-A                             | ≥250 V                |

| CDM, STD - JESD22-C101-C                            | ≥1250 V               |

| Thermal Resistance                                  |                       |

| $\theta_{JC}$                                       | 11.5°C/W              |

| θ <sub>JA</sub> , No Airflow, 4 layer JEDEC         | 19.1°C/W              |

| For soldering specifications: see product folder at |                       |

| www.ti.com                                          |                       |

| http://www.ti.com/lit/SNOA549                       |                       |

http://www.ti.com/lit/SNOA549

- (1) "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. Absolute Maximum Numbers are specified for a junction temperature range of -40°C to +125°C. Models are validated to Maximum Operating Voltages only.

- (2) If Military/Aérospace specified devices are required, please contact the Texas Instruments Sales Office / Distributors for availability and specifications.

- (3) Measured at default SD\_TH settings

### **Recommended Operating Conditions**

|                                        | Min   | Тур | Max   | Units |

|----------------------------------------|-------|-----|-------|-------|

| Supply Voltage                         |       |     |       |       |

| V <sub>DD</sub> to GND                 | 2.375 | 2.5 | 2.625 | V     |

| Ambient Temperature                    | -10   | 25  | +85   | °C    |

| SMBus (SDA, SCL)                       |       |     | 3.6   | V     |

| Supply Noise Tolerance up to 50Mhz (1) |       |     | 100   | mV pp |

(1) Allowed supply noise (mV<sub>P-P</sub> sine wave) under typical conditions.

#### **Electrical Characteristics**

Over recommended operating supply and temperature ranges with default register settings unless other specified.

| Symbol                           | Parameter                            | Conditions                                                                                                     | Min  | Тур                   | Max  | Units      |

|----------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------|------|-----------------------|------|------------|

| POWER (3)                        | ·                                    |                                                                                                                |      |                       |      |            |

| PD                               | Power Dissipation                    | EQX=Float, DEX=0, VOD=1Vpp<br>,PRSNT=0                                                                         |      | 800                   | 1000 | mW         |

|                                  | ·                                    | PRSNT=1, ENSMB=0                                                                                               |      | 4                     | 8    | mW         |

| LVCMOS / LVTTL DC                | SPECIFICATIONS                       |                                                                                                                |      |                       |      |            |

| V <sub>IH</sub>                  | High Level Input<br>Voltage          | (4)                                                                                                            | 2    |                       | 3.6  | V          |

| V <sub>IL</sub>                  | Low Level Input<br>Voltage           | (4)                                                                                                            | 0    |                       | 0.8  | V          |

| V <sub>OH</sub>                  | High Level Output<br>Voltage         | SMBUS open drain V <sub>OH</sub> set by pullup Resistor                                                        |      |                       |      | V          |

| V <sub>OL</sub>                  | Low Level Output<br>Voltage          | I <sub>OL</sub> = 4mA                                                                                          |      |                       | 0.4  | V          |

| I <sub>IH</sub>                  | Input High Current                   | V <sub>IN</sub> = 3.6V , LVCMOS                                                                                | -15  |                       | +15  |            |

|                                  |                                      | V <sub>IN</sub> = 3.6V , w/<br>FLOAT,PULLDOWN input                                                            | -15  |                       | +120 | μΑ         |

| I <sub>IL</sub>                  | Input Low Current                    | V <sub>IN</sub> = 0V                                                                                           | -15  |                       | +15  |            |

|                                  |                                      | V <sub>IN</sub> = 0V, w/FLOAT input                                                                            | -80  |                       | +15  | μA         |

| CML RECEIVER INPUT               | TS (IN_n+, IN_n-)                    |                                                                                                                |      |                       |      |            |

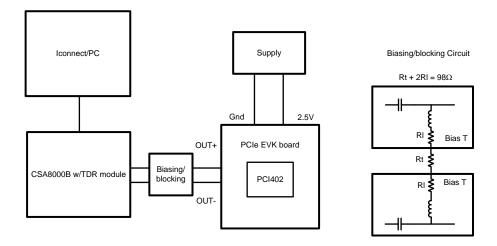

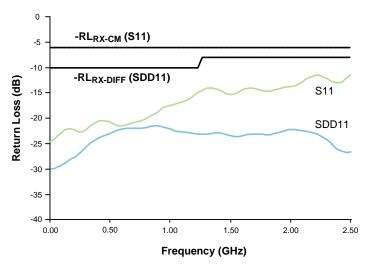

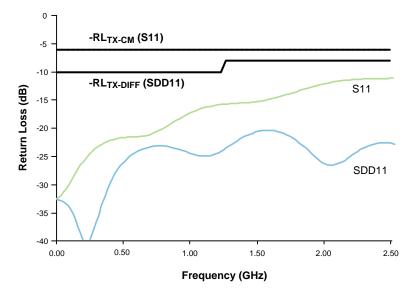

| RL <sub>RX-DIFF</sub>            | Rx package plus Si                   | 0.05GHz – 1.25GHz <sup>(5)</sup>                                                                               |      | -21                   | dB   |            |

|                                  | differential return loss             | 1.25GHz – 2.5GHz <sup>(5)</sup>                                                                                |      | -20                   |      |            |

| RL <sub>RX-CM</sub>              | Common mode Rx return loss           | 0.05GHz - 2.5GHz <sup>(5)</sup>                                                                                |      | -11.5                 |      | dB         |

| Z <sub>RX-DC</sub>               | Rx DC common mode impedance          | Tested at VDD=0                                                                                                | 40   | 50                    | 60   | Ω          |

| Z <sub>RX-DIFF-DC</sub>          | Rx DC differential impedance         | Tested at VDD=0                                                                                                | 85   | 100                   | 115  | Ω          |

| V <sub>RX-DIFF-DC</sub>          | Differential Rx peak to peak voltage | Tested at DC, TXIDLEx=0                                                                                        | 0.10 |                       | 1.2  | V          |

| Z <sub>RX-HIGH-IMP-DC</sub> -POS | DC Input CM impedance for V>0        | Vin = 0 to 200 mV,<br>RXDETA/B = 0,<br>ENSMB = 0, VDD=2.625                                                    | 50   |                       |      | ΚΩ         |

| V <sub>RX-IDLE-DET-DIFF-PP</sub> | Electrical Idle detect threshold     | SD_TH = float, see Table 5,                                                                                    | 40   |                       | 175  | $mV_{P-P}$ |

| LPDS OUTPUTS (OUT                | _n+, OUT_n-)                         | -                                                                                                              |      |                       |      |            |

| V <sub>TX-DIFF-PP</sub>          | Output Voltage Swing                 | Differential measurement with OUT_n+ and OUT_n- terminated by $50\Omega$ to GND AC-Coupled, Figure 4, $^{(3)}$ | 800  | 1000                  | 1200 | $mV_{P-P}$ |

| V <sub>OCM</sub>                 | Output Common-Mode<br>Voltage        | Single-ended measurement DC-Coupled with $50\Omega$ termination, <sup>(1)</sup>                                |      | V <sub>DD</sub> - 1.4 |      | V          |

<sup>(1)</sup> Typical values represent most likely parametric norms at V<sub>DD</sub> = 2.5V, T<sub>A</sub> = 25°C., and at the Recommended Operation Conditions at the time of product characterization and are not ensured.

Submit Documentation Feedback

Copyright © 2010–2013, Texas Instruments Incorporated

<sup>(2)</sup> The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

<sup>(3)</sup> Measured with DEM Select pins configured for 1000mV VOD, see De-emphasis table.

<sup>(4)</sup> Input edge rate for LVCMOS/FLOAT inputs must be 50ns minimum from 10-90%.

<sup>(5)</sup> Input Return Loss also uses the setup shown in Figure 6. The blocking / biasing circuit is replaced with a simple AC coupling capacitor for each input to emulate a typical PCIe application.

<sup>(6)</sup> Measured at package pins of receiver. Less than 40mV is IDLE, greater than 175mV is ACTIVE. SD\_TH pin connected with resistor to GND overrides this default setting.

#### **Electrical Characteristics (continued)**

Over recommended operating supply and temperature ranges with default register settings unless other specified.

| Symbol                                       | Parameter                                                                             | Conditions                                                              | Min | Тур  | Max  | Units  |

|----------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----|------|------|--------|

| V <sub>TX-DE-RATIO-3.5</sub>                 | Tx de-emphasis level ratio                                                            | VOD = 1000 mV, DEM1 = GND,<br>DEM0 = VDD, (1),                          |     | 3.5  |      | dB     |

| V <sub>TX-DE-RATIO-6</sub>                   | Tx de-emphasis level ratio                                                            | VOD = 1000 mV, DEM1 = VDD,<br>DEM0 = GND, (1),                          |     | 6    |      | dB     |

| T <sub>TX-HF-DJ-DD</sub>                     | Tx Dj > 1.5 Mhz                                                                       | (8)                                                                     |     |      | 0.15 | UI     |

| T <sub>TX-LF-RMS</sub>                       | Tx RMS jitter < 1.5Mhz                                                                | (8)                                                                     |     |      | 3.0  | ps RMS |

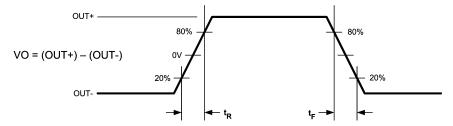

| T <sub>TX-RISE-FALL</sub>                    | Transmitter Rise/ Fall Time                                                           | 20% to 80% of differential output voltage, Figure 3                     | 50  | 67   |      | ps     |

| T <sub>RF-MISMATCH</sub>                     | Tx rise/fall mismatch                                                                 | 20% to 80% of differential output voltage <sup>(1)</sup> <sup>(9)</sup> |     | 0.01 | 0.1  | UI     |

| RL <sub>TX-DIFF</sub>                        | Differential Output                                                                   | 0.05- 1.25 Ghz, See Figure 6                                            |     | -23  |      | dB     |

|                                              | Return Loss                                                                           | 1.25- 2.5 Ghz, See Figure 6                                             |     | -20  |      | dB     |

| RL <sub>TX-CM</sub>                          | Common Mode Return<br>Loss                                                            | 0.05- 2.5 Ghz, See Figure 6                                             |     | -11  |      | dB     |

| Z <sub>TX-DIFF-DC</sub>                      | DC differential Tx impedance                                                          |                                                                         |     | 100  |      | Ω      |

| V <sub>TX-CM-AC-PP</sub>                     | Tx AC common mode voltage                                                             |                                                                         |     |      | 100  | mVpp   |

| I <sub>TX-SHORT</sub>                        | transmitter short circuit current limit                                               | Total current transmitter can supply when shorted to VDD or GND         |     |      | 90   | mA     |

| V <sub>TX-CM-DC-</sub> ACTIVE-IDLE-<br>DELTA | Absolute Delta of DC<br>Common Mode Voltage<br>during L0 and electrical<br>Idle       |                                                                         |     |      | 40   | mV     |

| V <sub>TX-CM-DC-</sub> LINE-DELTA            | Absolute Delta of DC<br>Common Mode Voltage<br>between Tx+ and Tx-                    |                                                                         |     |      | 25   | mV     |

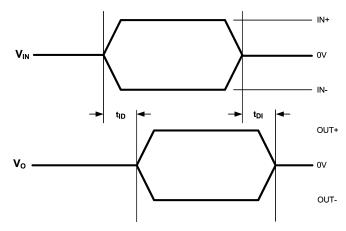

| T <sub>TX-IDLE-SET-TO</sub> -IDLE            | Max time to transition<br>to valid diff signaling<br>after leaving Electrical<br>Idle | VIN = 800 mVp-p, 5 Gbps,<br>Figure 5                                    |     | 6.5  | 9.5  | nS     |

| T <sub>TX-IDLE-TO</sub> -DIFF-DATA           | Max time to transition<br>to valid diff signaling<br>after leaving Electrical<br>Idle | VIN = 800 mVp-p, 5 Gbps,<br>Figure 5                                    |     | 5.5  | 8    | nS     |

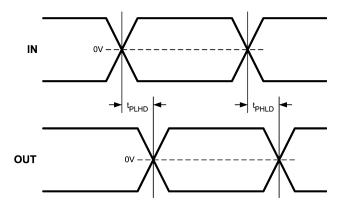

| T <sub>PDEQ</sub>                            | Differential Propagation<br>Delay                                                     | EQ = 11,<br>+4.0 dB @ 2.5 GHz , Figure 4                                | 150 | 200  | 250  | ps     |

| T <sub>PD</sub>                              | Differential Propagation<br>Delay                                                     | EQ = FF,<br>Equalizer Bypass, Figure 4<br>(10) (11)                     | 120 | 170  | 220  | ps     |

| T <sub>LSK</sub>                             | Lane to Lane Skew in a Single Part                                                    | $T_A = 25C, V_{DD} = 2.5V$                                              |     |      | 27   | ps     |

<sup>(7)</sup> Measured with a repeating K28.5 pattern at a data rate of 2.5 Gbps and 5.0 Gbps.

PCle 2.0 transmit jitter specifications - actual device jitter is much less. Actual device Rj and Dj has been characterized and specified with test loads outlined in the EQUALIZATION and DE-EMPHASIS sections of the Electrical Characteristics table.

<sup>(9)</sup> Specified by device characterization

<sup>(10)</sup> Propagation Delay measurements will change slightly based on the level of EQ selected. EQ Bypass will result in the shortest

propagation delays.

(11) Propagation Delay measurements for Part to Part skew are all based on devices operating under indentical temperature and supply voltage conditions.

<sup>(12)</sup> Specified by device characterization

#### **Electrical Characteristics (continued)**

Over recommended operating supply and temperature ranges with default register settings unless other specified.

| Symbol            | Parameter                                                                                                                                                | Parameter Conditions                                                                                                              |                                                                                                | Тур  | Max  | Units             |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|-------------------|

| T <sub>PPSK</sub> | Part to Part<br>Propagation Delay<br>Skew                                                                                                                | $T_A = 25C, V_{DD} = 2.5V$                                                                                                        |                                                                                                |      | 35   | ps                |

| EQUALIZATION      | ·                                                                                                                                                        |                                                                                                                                   |                                                                                                |      |      |                   |

| DJE1              | Residual Deterministic  Jitter at 5 Gbps  42" of 5 mil stripline FR4, EQ1,0=F,1; K28.5 pattern, DEMx=0, Tx Launch Amplitude 1.0 Vp-p, SD TH=F. (13) (14) |                                                                                                                                   |                                                                                                | 0.02 | 0.09 | UI <sub>P-P</sub> |

| DJE2              | Residual Deterministic<br>Jitter at 2.5 Gbps                                                                                                             | 42" of 5 mil stripline FR4,<br>EQ1,0=F,1; K28.5 pattern,<br>DEMx=0, Tx Launch Amplitude 1.0<br>Vp-p, SD_TH=F. (13) (14)           |                                                                                                | 0.02 | 0.04 | UI <sub>P-P</sub> |

| DJE3              | Residual Deterministic<br>Jitter at 5 Gbps                                                                                                               | 7 meters of 24 AWG PCIe cable,<br>EQ1,0=1,0; K28.5 pattern,<br>DEMx=0, Tx Launch Amplitude 1.0<br>Vp-p, SD_TH=F. (13) (14)        | 7 meters of 24 AWG PCIe cable,<br>EQ1,0=1,0; K28.5 pattern,<br>DEMx=0. Tx Launch Amplitude 1.0 |      |      |                   |

| DJE4              | Residual Deterministic<br>Jitter at 2.5 Gbps                                                                                                             | nistic 7 meters of 24 AWG PCIe cable,<br>EQ1,0=1,0; K28.5 pattern,<br>DEMx=0, Tx Launch Amplitude 1.0<br>Vp-p, SD_TH=F. (13) (14) |                                                                                                | 0.03 | 0.07 | UI <sub>P-P</sub> |

| RJ                | Random Jitter                                                                                                                                            | Tx Launch Amplitude 1.0 Vp-p,<br>SD_TH=F, Repeating 1100b<br>(D24.3) pattern. (13)                                                |                                                                                                | <0.5 |      | psrms             |

| DE-EMPHASIS       | ·                                                                                                                                                        |                                                                                                                                   |                                                                                                |      |      |                   |

| DJD1              | Residual Deterministic<br>Jitter at 5 Gbps                                                                                                               | 28" of 5 mil stripline FR4,<br>EQ1,0=F,F; K28.5 pattern,<br>DEM1,0=F,1; Tx Launch<br>Amplitude 1.0 Vp-p, SD_TH=F. (13)            |                                                                                                | 0.02 | 0.09 | UI <sub>P-P</sub> |

| DJD2              | Residual Deterministic<br>Jitter at 2.5 Gbps                                                                                                             | 28" of 5 mil microstrip FR4,<br>EQ1,0=F,F; K28.5 pattern,<br>DEM1,0=F,0; Tx Launch<br>Amplitude 1.0 Vp-p, SD_TH=F. (15)           |                                                                                                | 0.03 | 0.05 | UI <sub>P-P</sub> |

| DJD3              | Residual Deterministic<br>Jitter at 5 Gbps                                                                                                               | 7 meters of 24 AWG PCIe cable,<br>EQ1,0=F,F; K28.5 pattern,<br>DEM1,0=F,1; Tx Launch<br>Amplitude 1.0 Vp-p, SD_TH=F. (15)<br>(16) |                                                                                                | 0.03 | 0.13 | UI <sub>P-P</sub> |

| DJD4              | Residual Deterministic<br>Jitter at 2.5 Gbps                                                                                                             | 7 meters of 24 AWG PCIe cable,<br>EQ1,0=F,F; K28.5 pattern,<br>DEM1,0=F,0; Tx Launch<br>Amplitude 1.0 Vp-p, SD_TH=F. (15)<br>(16) |                                                                                                | 0.04 | 0.06 | UI <sub>P-P</sub> |

<sup>(13)</sup> Typical values represent most likely parametric norms at V<sub>DD</sub> = 2.5V, T<sub>A</sub> = 25°C., and at the Recommended Operation Conditions at the time of product characterization and are not ensured.

#### Electrical Characteristics — Serial Management Bus Interface

Over recommended operating supply and temperature ranges unless other specified.

| Symbol          | Parameter                     | Conditions | Min | Тур | Max | Units |

|-----------------|-------------------------------|------------|-----|-----|-----|-------|

| SERIAL BUS II   | NTERFACE DC SPECIFICATIONS    |            |     |     |     |       |

| V <sub>IL</sub> | Data, Clock Input Low Voltage |            |     |     | 0.8 | V     |

<sup>(14)</sup> Residual DJ measurements subtract out deterministic jitter present at the generator outputs. For 2.5 Gbps generator Dj = 0.0275 UI and for 5.0 Gbps generator Dj = 0.035 UI.

<sup>(15)</sup> Typical values represent most likely parametric norms at V<sub>DD</sub> = 2.5V, T<sub>A</sub> = 25°C., and at the Recommended Operation Conditions at the time of product characterization and are not ensured.

<sup>(16)</sup> Residual DJ measurements subtract out deterministic jitter present at the generator outputs. For 2.5 Gbps generator Dj = 0.0275 UI and for 5.0 Gbps generator Dj = 0.035 UI.

### Electrical Characteristics — Serial Management Bus Interface (continued)

Over recommended operating supply and temperature ranges unless other specified.

| Symbol                 | Parameter                                                                                          | Conditions                     | Min   | Тур  | Max  | Units |

|------------------------|----------------------------------------------------------------------------------------------------|--------------------------------|-------|------|------|-------|

| V <sub>IH</sub>        | Data, Clock Input High Voltage                                                                     |                                | 2.1   |      | 3.6  | V     |

| I <sub>PULLUP</sub>    | Current Through Pull-Up Resistor or Current Source                                                 | High Power Specification       | 4     |      |      | mA    |

| $V_{DD}$               | Nominal Bus Voltage                                                                                |                                | 2.375 |      | 3.6  | V     |

| I <sub>LEAK-Bus</sub>  | Input Leakage Per Bus Segment                                                                      | (1)                            | -200  |      | +200 | μΑ    |

| I <sub>LEAK-Pin</sub>  | Input Leakage Per Device Pin                                                                       |                                |       | -15  |      | μΑ    |

| C <sub>I</sub>         | Capacitance for SDA and SCL                                                                        | (1) (2)                        |       |      | 10   | pF    |

| R <sub>TERM</sub>      | External Termination Resistance pull to V <sub>DD</sub> = 2.5V ± 5% OR 3.3V ±                      | Pullup $V_{DD} = 3.3V$ ,       |       | 2000 |      | Ω     |

|                        | 10%                                                                                                | Pullup V <sub>DD</sub> = 2.5V, |       | 1000 |      | Ω     |

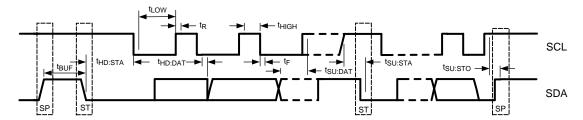

| SERIAL BUS             | INTERFACE TIMING SPECIFICATION                                                                     | IS. See Figure 7               |       |      | 1    |       |

| FSMB                   | Bus Operating Frequency                                                                            | (4)                            | 10    |      | 100  | kHz   |

| TBUF                   | Bus Free Time Between Stop and Start Condition                                                     |                                | 4.7   |      |      | μs    |

| THD:STA                | Hold time after (Repeated) Start<br>Condition. After this period, the first<br>clock is generated. | At I <sub>PULLUP</sub> , Max   | 4.0   |      |      | μs    |

| TSU:STA                | Repeated Start Condition Setup<br>Time                                                             |                                | 4.7   |      |      | μs    |

| TSU:STO                | Stop Condition Setup Time                                                                          |                                | 4.0   |      |      | μs    |

| THD:DAT                | Data Hold Time                                                                                     |                                | 300   |      |      | ns    |

| TSU:DAT                | Data Setup Time                                                                                    |                                | 250   |      |      | ns    |

| T <sub>TIMEOUT</sub>   | Detect Clock Low Timeout                                                                           | (5)                            | 25    |      | 35   | ms    |

| $T_{LOW}$              | Clock Low Period                                                                                   |                                | 4.7   |      |      | μs    |

| T <sub>HIGH</sub>      | Clock High Period                                                                                  | (5)                            | 4.0   |      | 50   | μs    |

| T <sub>LOW</sub> :SEXT | Cumulative Clock Low Extend Time (Slave Device)                                                    | (5)                            |       |      | 2    | ms    |

| t <sub>F</sub>         | Clock/Data Fall Time                                                                               | (5)                            |       |      | 300  | ns    |

| t <sub>R</sub>         | Clock/Data Rise Time                                                                               | (5)                            |       |      | 1000 | ns    |

| t <sub>POR</sub>       | Time in which a device must be operational after power-on reset                                    | (5)                            |       |      | 500  | ms    |

- (1) Recommended value. Parameter not tested in production.

- (2) Recommended maximum capacitance load per bus segment is 400pF.

- (3) Maximum termination voltage should be identical to the device supply voltage.

- (4) Compliant to SMBus 2.0 physical layer specification. See System Management Bus (SMBus) Specification Version 2.0, section 3.1.1 SMBus common AC specifications for details.

- (5) Compliant to SMBus 2.0 physical layer specification. See System Management Bus (SMBus) Specification Version 2.0, section 3.1.1 SMBus common AC specifications for details.

#### **TIMING DIAGRAMS**

Figure 3. CML Output Transition Times

Figure 4. Propagation Delay Timing Diagram

Figure 5. Idle Timing Diagram

Figure 6. Input and Output Return Loss Setup

Figure 7. SMBus Timing Parameters

#### SYSTEM MANAGEMENT BUS (SMBUS) AND CONFIGURATION REGISTERS

The System Management Bus interface is compatible to SMBus 2.0 physical layer specification. ENSMB must be pulled high to enable SMBus mode and allow access to the configuration registers.

The DS50PCl402 has the AD[3:0] inputs in SMBus mode. These pins are the user set SMBus slave address inputs. The AD[3:0] pins have internal pull-down. When left floating or pulled low the AD[3:0] = 0000'b, the device default address byte is A0'h. Based on the SMBus 2.0 specification, the DS50PCl402 has a 7-bit slave address of 1010000'b. The LSB is set to 0'b (for a WRITE), thus the 8-bit value is 1010 0000'b or A0'h. The device address byte can be set with the use of the AD[3:0] inputs. Below are some examples.

AD[3:0] = 0001'b, the device address byte is A2'h

AD[3:0] = 0010'b, the device address byte is A4'h

AD[3:0] = 0100'b, the device address byte is A8'h

AD[3:0] = 1000'b, the device address byte is B0'h

The SDA, SCL pins are 3.3V tolerant, but are not 5V tolerant. External pull-up resistor is required on the SDA. The resistor value can be from 1 k $\Omega$  to 5 k $\Omega$  depending on the voltage, loading and speed. The SCL may also require an external pull-up resistor and it depends on the Host that drives the bus.

#### TRANSFER OF DATA VIA THE SMBus

During normal operation the data on SDA must be stable during the time when SCL is High.

There are three unique states for the SMBus:

**START:** A High-to-Low transition on SDA while SCL is High indicates a message START condition.

**STOP:** A Low-to-High transition on SDA while SCL is High indicates a message STOP condition.

**IDLE:** If SCL and SDA are both High for a time exceeding  $t_{BUF}$  from the last detected STOP condition or if they are High for a total exceeding the maximum specification for  $t_{HIGH}$  then the bus will transfer to the IDLE state.

#### **SMBus TRANSACTIONS**

The device supports WRITE and READ transactions. See Register Description table for register address, type (Read/Write, Read Only), default value and function information.

When SMBus is enabled, the DS50PCI402 **must use one of the following De-emphasis settings** (Table 9). The driver de-emphasis value is set on a per channel basis using 8 different registers. Each register (0x11, 0x18, 0x1F, 0x26, 0x2E, 0x35, 0x3C, 0x43) requires one of the following De-emphasis settings when in SMBus mode. See Table 5 for suggested DE settings at 2.5 and 5.0 Gbps operation.

Table 9. De-Emphasis Register Settings (must write one of the following when in SMBus mode)

| De-Emphasis Value | Register Setting |

|-------------------|------------------|

| 0.0 dB            | 0x01             |

| -3.5 dB           | 0xE8             |

| -6 dB             | 0x88             |

| -9 dB             | 0x90             |

## Table 9. De-Emphasis Register Settings (must write one of the following when in SMBus mode) (continued)

| De-Emphasis Value | Register Setting |

|-------------------|------------------|

| -12 dB            | 0xA0             |

#### WRITING A REGISTER

To write a register, the following protocol is used (see SMBus 2.0 specification).

- 1. The Host drives a START condition, the 7-bit SMBus address, and a "0" indicating a WRITE.

- 2. The Device (Slave) drives the ACK bit ("0").

- 3. The Host drives the 8-bit Register Address.

- 4. The Device drives an ACK bit ("0").

- 5. The Host drive the 8-bit data byte.

- 6. The Device drives an ACK bit ("0").

- 7. The Host drives a STOP condition.

The WRITE transaction is completed, the bus goes IDLE and communication with other SMBus devices may now occur.

#### READING A REGISTER

To read a register, the following protocol is used (see SMBus 2.0 specification).

- 1. The Host drives a START condition, the 7-bit SMBus address, and a "0" indicating a WRITE.

- 2. The Device (Slave) drives the ACK bit ("0").

- 3. The Host drives the 8-bit Register Address.

- 4. The Device drives an ACK bit ("0").

- 5. The Host drives a START condition.

- 6. The Host drives the 7-bit SMBus Address, and a "1" indicating a READ.

- 7. The Device drives an ACK bit "0".

- 8. The Device drives the 8-bit data value (register contents).

- 9. The Host drives a NACK bit "1" indicating end of the READ transfer.

- 10. The Host drives a STOP condition.