# CD4019BC Quad AND-OR Select Gate

## FAIRCHILD

SEMICONDUCTOR

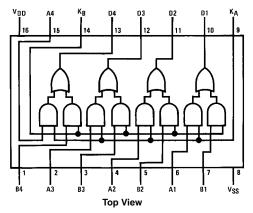

# CD4019BC Quad AND-OR Select Gate

### **General Description**

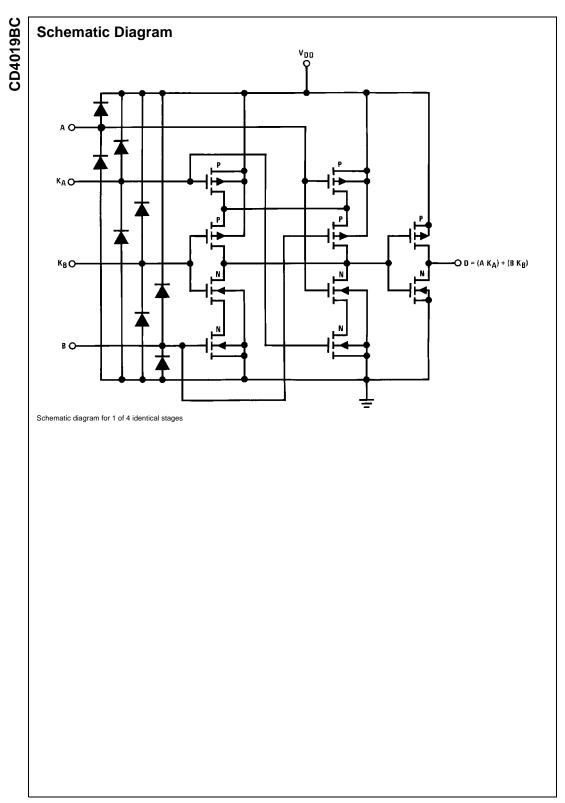

The CD4019BC is a complementary MOS quad AND-OR select gate. Low power and high noise margin over a wide voltage range is possible through implementation of N- and P-channel enhancement mode transistors. These complementary MOS (CMOS) transistors provide the building blocks for the 4 "AND-OR select" gate configurations, each consisting of two 2-input AND gates driving a single 2-input OR gate. Selection is accomplished by control bits K<sub>A</sub> and K<sub>B</sub>. All inputs are protected against static discharge damage.

### Features

- Wide supply voltage range: 3.0V to 15V

- High noise immunity: 0.45 V<sub>DD</sub> (typ.)

- Low power TTL compatibility: Fan out of 2 driving 74L or 1 driving 74LS

October 1987

Revised April 2002

### Applications

- AND-OR select gating

- Shift-right/shift-left registers

- True/complement selection

- AND/OR/EXCLUSIVE-OR selection

### **Ordering Code:**

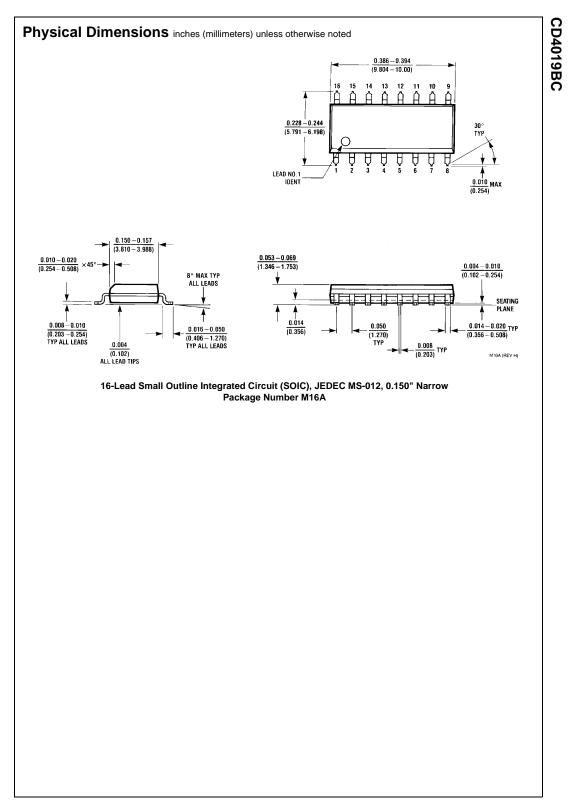

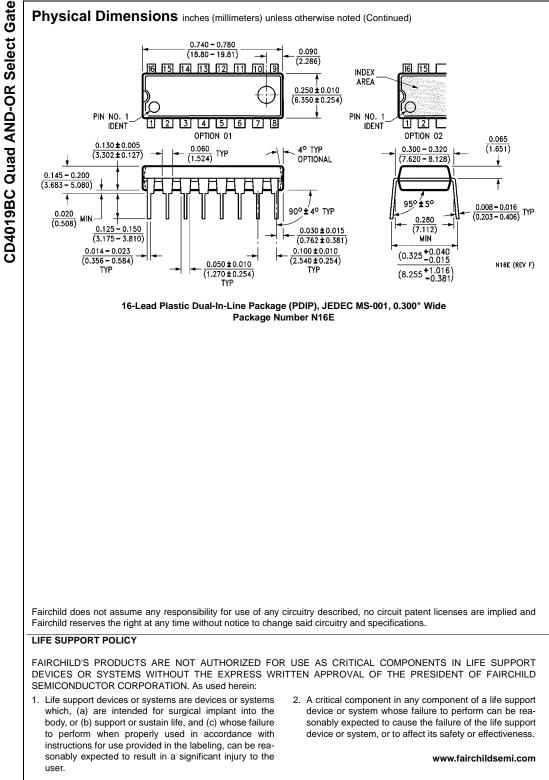

| Order Number             | Package Number              | Package Description                                                          |

|--------------------------|-----------------------------|------------------------------------------------------------------------------|

| CD4019BCM                | M16A                        | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow |

| CD4019BCN                | N16E                        | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide       |

| Devices also available i | in Tape and Reel. Specify b | by appending the suffix letter "X" to the ordering code.                     |

### **Connection Diagram**

© 2002 Fairchild Semiconductor Corporation DS005952

### Absolute Maximum Ratings(Note 1)

| (Note 2)                            |                                  |

|-------------------------------------|----------------------------------|

| Supply Voltage (V <sub>DD</sub> )   | -0.5V to +18V                    |

| Input Voltage (V <sub>IN</sub> )    | -0.5V to V <sub>DD</sub> $+0.5V$ |

| Storage Temperature Range $(T_S)$   | -65°C to +150°C                  |

| Power Dissipation (P <sub>D</sub> ) |                                  |

| Dual-In-Line                        | 700 mW                           |

| Small Outline                       | 500 mW                           |

| Lead Temperature (T <sub>L</sub> )  |                                  |

| (Soldering, 10 seconds)             | 260°C                            |

### Recommended Operation Conditions (Note 2)

DC Supply Voltage (V<sub>DD</sub>) Input Voltage (V<sub>IN</sub>)

+3V to +15V 0V to V<sub>DD</sub>V CD4019BC

mended Operating Conditions" and "Electrical Characteristics" provide conditions for actual device operation. \\

Note 2:  $V_{SS} = 0V$  unless otherwise specified.

### DC Electrical Characteristics (Note 3)

| Symbol          | Parameter         | Conditions                                     | -5    | –55°C |       | +25°C             |       |       | +125°C |       |

|-----------------|-------------------|------------------------------------------------|-------|-------|-------|-------------------|-------|-------|--------|-------|

| Symbol          |                   |                                                | Min   | Max   | Min   | Тур               | Max   | Min   | Max    | Units |

| I <sub>DD</sub> | Quiescent Device  | $V_{DD} = 5V$                                  |       | 0.25  |       | 0.25              | 1     |       | 7.5    |       |

|                 | Current           | $V_{DD} = 10V$                                 |       | 0.5   |       | 0.5               | 2     |       | 15     | μA    |

|                 |                   | $V_{DD} = 15V$                                 |       | 1.0   |       | 1.0               | 4     |       | 30     |       |

| V <sub>OL</sub> | LOW Level         | I <sub>O</sub>   < 1 μA                        |       |       |       |                   |       |       |        |       |

|                 | Output Voltage    | $V_{DD} = 5V$                                  |       | 0.05  |       | 0                 | 0.05  |       | 0.05   |       |

|                 |                   | $V_{DD} = 10V$                                 |       | 0.05  |       | 0                 | 0.05  |       | 0.05   | V     |

|                 |                   | $V_{DD} = 15V$                                 |       | 0.05  |       | 0                 | 0.05  |       | 0.05   |       |

| V <sub>OH</sub> | HIGH Level        | I <sub>O</sub>   < 1 μA                        |       |       |       |                   |       |       |        |       |

|                 | Output Voltage    | $V_{DD} = 5V$                                  | 4.95  |       | 4.95  | 5                 |       | 4.95  |        |       |

|                 |                   | $V_{DD} = 10V$                                 | 9.95  |       | 9.95  | 10                |       | 9.95  |        | V     |

|                 |                   | $V_{DD} = 15V$                                 | 14.95 |       | 14.95 | 15                |       | 14.95 |        |       |

| VIL             | LOW Level         | $V_{DD} = 5V, V_O = 0.5V \text{ or } 4.5V$     |       | 1.5   |       | 2                 | 1.5   |       | 1.5    |       |

|                 | Input Voltage     | $V_{DD} = 10V, V_O = 1.0V \text{ or } 9.0V$    |       | 3.0   |       | 4                 | 3.0   |       | 3.0    | V     |

|                 |                   | $V_{DD} = 15V, V_{O} = 1.5V \text{ or } 13.5V$ |       | 4.0   |       | 6                 | 4.0   |       | 4.0    |       |

| V <sub>IH</sub> | HIGH Level        | $V_{DD} = 5V, V_O = 0.5V \text{ or } 4.5V$     | 3.5   |       | 3.5   | 3                 |       | 3.5   |        |       |

|                 | Input Voltage     | $V_{DD} = 10V, V_O = 1.0V \text{ or } 9.0V$    | 7.0   |       | 7.0   | 6                 |       | 7.0   |        | V     |

|                 |                   | $V_{DD} = 15V, V_{O} = 1.5V \text{ or } 13.5V$ | 11.0  |       | 11.0  | 9                 |       | 11.0  |        |       |

| I <sub>OL</sub> | LOW Level Output  | $V_{DD} = 5V, V_{O} = 0.4V$                    | 0.64  |       | 0.51  | 1                 |       | 0.36  |        |       |

|                 | Current (Note 4)  | $V_{DD} = 10V, V_O = 0.5V$                     | 1.6   |       | 1.3   | 2.5               |       | 0.9   |        | mA    |

|                 |                   | $V_{DD} = 15V, V_{O} = 1.5V$                   | 4.2   |       | 3.4   | 10                |       | 2.4   |        |       |

| I <sub>OH</sub> | HIGH Level Output | $V_{DD} = 5V, V_{O} = 4.6V$                    | -0.25 |       | -0.2  | -0.4              |       | -0.14 |        |       |

|                 | Current (Note 4)  | $V_{DD} = 10V, V_O = 9.5V$                     | -0.62 |       | -0.5  | -1.0              |       | -0.35 |        | mA    |

|                 |                   | $V_{DD} = 15V, V_O = 13.5V$                    | -1.8  |       | -1.5  | -3.0              |       | -1.1  |        |       |

| I <sub>IN</sub> | Input Current     | $V_{DD} = 15V, V_{IN} = 0V$                    |       | -0.1  |       | -10 <sup>-5</sup> | -0.10 |       | -1.0   | μA    |

|                 |                   | $V_{DD} = 15V, V_{IN} = 15V$                   |       | 0.1   |       | 10 <sup>-5</sup>  | 0.10  |       | 1.0    | μΑ    |

Note 3:  $V_{SS} = 0V$  unless otherwise specified.

Note 4:  $I_{\mbox{OH}}$  and  $I_{\mbox{OL}}$  are tested one output at a time.

| υ |

|---|

| Ω |

| ດ |

| Σ |

| 9 |

| Z |

|   |

| C |

| _ |

### AC Electrical Characteristics (Note 5)

| Symbol             | Parameter          | Conditions                               | Min | Тур | Max | Units |

|--------------------|--------------------|------------------------------------------|-----|-----|-----|-------|

| t <sub>PHL</sub> , | Propagation Delay, | $V_{DD} = 5V$                            |     | 100 | 300 |       |

| t <sub>PLH</sub>   | Input to Output    | $V_{DD} = 10V$                           |     | 50  | 120 | ns    |

|                    |                    | $V_{DD} = 15V$                           |     | 45  | 100 |       |

| t <sub>THL</sub>   | HIGH-to-LOW Level  | $V_{DD} = 5V$                            |     | 100 | 200 |       |

|                    | Transition Time    | $V_{DD} = 10V$                           |     | 50  | 100 | ns    |

|                    |                    | $V_{DD} = 15V$                           |     | 40  | 80  |       |

| t <sub>TLH</sub>   | LOW-to-HIGH Level  | $V_{DD} = 5V$                            |     | 150 | 300 |       |

|                    | Transition Time    | $V_{DD} = 10V$                           |     | 70  | 140 | ns    |

|                    |                    | $V_{DD} = 15V$                           |     | 50  | 100 |       |

| C <sub>IN</sub>    | Input Capacitance  | All A and B Inputs                       |     | 5   | 7.5 | 5 L   |

|                    |                    | K <sub>A</sub> and K <sub>B</sub> Inputs |     | 10  | 15  | pF    |

Note 5: AC Parameters are guaranteed by DC correlated testing.